# HRF-AT4521 31.0 dB, DC - 2.5GHz, 5 Bit Serial Digital Attenuator

The Honeywell HRF-AT4521 is a 5-bit digital attenuator that is ideal for use in broadband communication system applications that require accuracy, speed and low power consumption. The HRF-AT4521 is manufactured with Honeywell's patented Silicon On Insulator (SOI) CMOS manufacturing technology, which provides the performance of GaAs with the economy and integration capabilities of conventional CMOS. These attenuators are DC coupled to improve lower operating frequency, frequency response and reduce the number of DC bias points required.

## FEATURES

- Very Low DC Power Consumption

- Attenuation In Steps From 1 dB To 31 dB

- Single Positive Power Supply Voltage

- Serial Data Interface

- 50 Ohm Impedance

- DC-coupled, bi-directional RF path

- Space Saving VQFN Surface Mount Packaging

- Lead-free, RoHS compliant and Green

# RF ELECTRICAL SPECIFICATIONS @ + 25°C

Results @  $V_{DD}$  = 5.0 +/- 10%,  $V_{SS}$  = 0 unless otherwise stated,  $Z_0$  = 50 Ohms Contact Honeywell for relative performance at other supply configurations

| Parameter                       | Test Condition                                                                          | Frequency                     | Minimum | Typical                                                                                     | Maximum           | Units          |

|---------------------------------|-----------------------------------------------------------------------------------------|-------------------------------|---------|---------------------------------------------------------------------------------------------|-------------------|----------------|

| Insertion Loss                  |                                                                                         | 1.0 GHz<br>2.0 GHz<br>2.5 GHz |         | 2.0<br>2.2<br>2.8                                                                           | 2.6<br>2.8<br>3.4 | dB<br>dB<br>dB |

| 1dB Compression                 | $V_{SS} = 0V$ , Input Power<br>$V_{SS} = - 3V$ , Input Power                            | 2.0 GHz<br>2.0 GHz            |         | 22<br>28                                                                                    |                   | dBm<br>dBm     |

| Input IP3                       | V <sub>SS</sub> = 0V<br>Two-tone inputs, up to +5 dBm<br>@ 0 dBm attenuation            | 2.0 GHz                       |         | 36                                                                                          |                   | dBm            |

| Input IP3                       | V <sub>ss</sub> = -3V<br>Two-tone inputs, up to + 5 dBm<br>@ 0 dBm attenuation          | 2.0 GHz                       |         | >36                                                                                         |                   | dBm            |

| Return Loss                     | Any Combination of Bits                                                                 |                               | -11     | -13                                                                                         |                   | dB             |

| Attenuation Accuracy            | All attenuation states1.0 GHzAll attenuation states2.0 GHzAll attenuation states2.5 GHz |                               | + 0.4   | + (0.25 + 2.5 %), - (0.10 + 5.0 %)<br>+ 0.45, - (0.20 + 8.0 %)<br>+ 0.35, - (-0.40 + 10.5%) |                   | dB<br>dB<br>dB |

| Trise, Tfall<br>Ton, Toff (Tpd) | 10% To 90%<br>50% Cntl To 90%/10%RF                                                     |                               |         | 10<br>15                                                                                    |                   | nS<br>nS       |

| T clock Period (Tprd)           | T high / T low = ½ minimum clock period                                                 |                               | 50      |                                                                                             |                   | nS             |

| T data set up (Tsup)            | Set up to rising edge of clock                                                          |                               | 5       |                                                                                             |                   | nS             |

| T data hold (Thld)              | Data hold after rising edge of clock                                                    |                               | 2       |                                                                                             |                   | nS             |

| T latch set up (Tlsup)          | Data set up to rising edge of OE                                                        |                               | 5       |                                                                                             |                   | nS             |

Note 1 - For higher accuracy designs, please consider HRF-AT4610/HRF-AT4611

HRF-AT4521 in VQFN Package

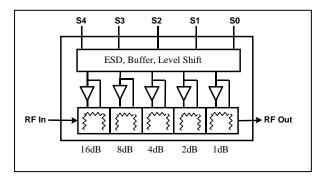

# FUNCTIONAL SCHEMATIC

# DC ELECTRICAL SPECIFICATIONS @ + 25°C

| Minimum          | Typical                       | Maximum                                          | Units                                                                      |

|------------------|-------------------------------|--------------------------------------------------|----------------------------------------------------------------------------|

| 3.3 <sup>1</sup> | 5.0                           | 5.5                                              | V                                                                          |

| -5.0             |                               |                                                  | V                                                                          |

|                  | <5.0                          | 50                                               | uA                                                                         |

| 0                |                               | 0.8                                              | V                                                                          |

| $V_{DD} - 0.8$   |                               | V <sub>DD</sub>                                  | V                                                                          |

|                  |                               | 10                                               | uA                                                                         |

|                  | 3.3 <sup>1</sup><br>-5.0<br>0 | 3.3 <sup>1</sup> 5.0           -5.0         <5.0 | 3.3 <sup>1</sup> 5.0         5.5           -5.0             0         <5.0 |

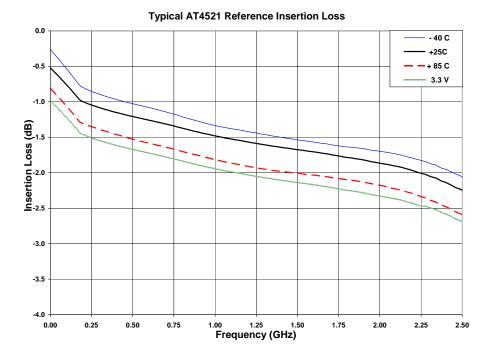

Note 1, the performance curves are for  $V_{DD}$  = +5.0 +/- 10%

## ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Parameter                  | Absolute Maximum                     | Units |

|----------------------------|--------------------------------------|-------|

| Input Power                | + 35                                 | dBm   |

| V <sub>DD</sub>            | +6.0                                 | V     |

| V <sub>SS</sub>            | -5.5                                 | V     |

| ESD Voltage <sup>2</sup>   | 400                                  | V     |

| Operating Temperature      | -40 To +85                           | Oo    |

| Storage Temperature        | -65 To +125                          | °C    |

| Moisture Sensitivity Level | Level 3 @ 260 <sup>0</sup> C         |       |

| Digital Inputs             | V <sub>DD</sub> +0.6 max to -0.6 min | V     |

Note 1 - Operation of this device beyond any of these parameters may cause permanent damage.

Note 2 - Although the HRF-AT4521 contains ESD protection circuitry on all digital inputs, precautions should be taken to ensure that the Absolute Maximum Ratings are not exceeded.

Latch-Up: Unlike conventional CMOS digital attenuators, Honeywell's HRF-AT4521 is immune to latch-up.

| Pin | Function | Pin | Function  |

|-----|----------|-----|-----------|

| 1   | VDD      | 9   | GROUND    |

| 2   | GROUND   | 10  | RF OUTPUT |

| 3   | RF INPUT | 11  | GROUND    |

| 4   | GROUND   | 12  | VSS       |

| 5   | GROUND   | 13  | GROUND    |

| 6   | GROUND   | 14  | OE        |

| 7   | GROUND   | 15  | CLK       |

| 8   | GROUND   | 16  | DATA      |

### **PIN CONFIGURATIONS**

Note: Bottom ground plate must be grounded for proper RF performance.

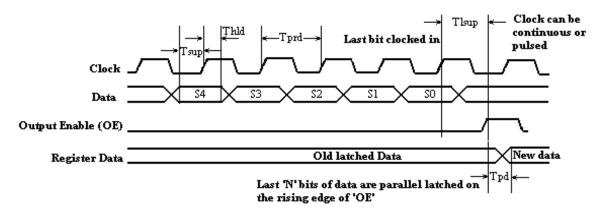

### SERIAL DATA LOAD

Serial data is shifted into the register on the rising edge of clock, MSB first. The state of "OE" will not affect the shifting of data. The rising edge of the "OE" signal will be the clock for the transfer of shifted data. Latched new data occurs one prop delay after the rising edge of "OE". See the Electrical Spec Table for AC parameters.

| S4                         | S3                         | S2                         | S1                              | S0                         | Output                                                            |

|----------------------------|----------------------------|----------------------------|---------------------------------|----------------------------|-------------------------------------------------------------------|

| 0<br>0<br>0<br>0<br>1<br>1 | 0<br>0<br>0<br>1<br>0<br>1 | 0<br>0<br>1<br>0<br>0<br>1 | 0<br>0<br>1<br>0<br>0<br>0<br>1 | 0<br>1<br>0<br>0<br>0<br>1 | Reference Input<br>1 dB<br>2 dB<br>4 dB<br>8 dB<br>16 dB<br>31 dB |

### **TRUTH TABLE**

Operation: Data on serial input D is clocked into internal registers on the low to high transition of the Clock signal (CK). The register output is enabled when Output Enable (OE) is in the low state. "0" = CMOS Low, "1" = CMOS High.

## **PERFORMANCE CURVES**

#### **Insertion Loss**

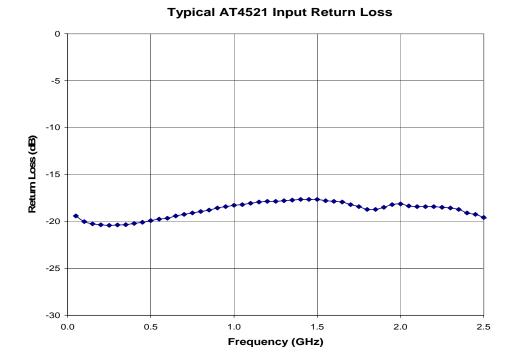

#### **Return Loss**

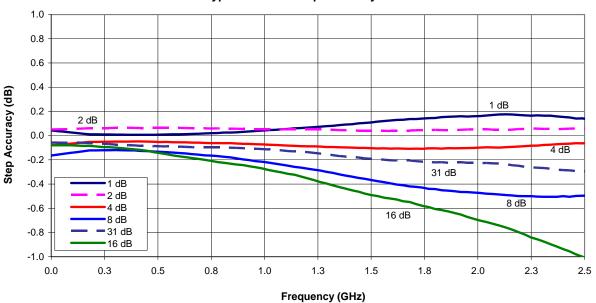

#### **Step Accuracy**

**Typical AT4521 Step Accuracy**

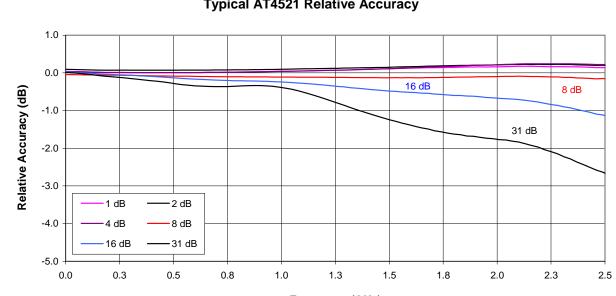

#### **Relative Accuracy**

#### **Typical AT4521 Relative Accuracy**

Frequency (GHz)

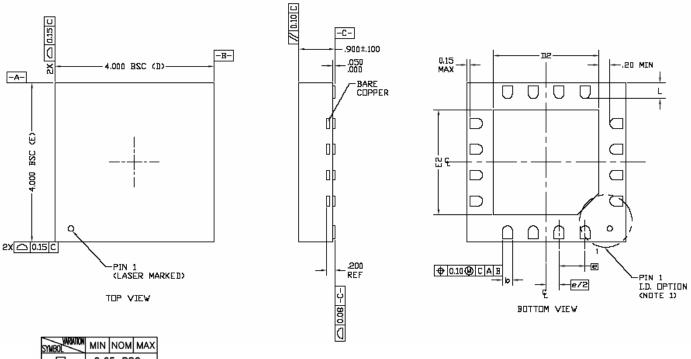

# PACKAGE OUTLINE DRAWING

SMB0

MMM

MIN

NOM

MAX

@

0.65

BSC

b

0.25

0.30

0.35

E2

2.40

2.50

2.60

D2

2.40

2.50

2.60

L

0.30

0.40

0.50

INTERNAL FEATURE

FUSE

LEAD

#### Notes

- 1. Pin 1 identifier can be a combination or a dot and/or chamfer.

- 2. Dimensions are in millimeters.

### **GREEN MATERIAL SET**

The –GR attenuators have a Green material set that can withstand a maximum soldering temperature of 260°C.

### LEAD FINISH

The package leads are Nickel Palladium Gold (NiPdAu). The configuration being manufactured and delivered today is lead-free RoHS compliant. Compliant packages have half-etch leadframes and have date codes of 0300 or greater.

# LEAD FREE QFN SURFACE MOUNT APPLICATION

Please see Application Note AN310 for assembly process recommendations. The maximum soldering temperature of the -GR is 260°C (-AU attenuators are 250 °C). Application Notes can be found at our website: www.honeywell.com/microwave

## **CIRCUIT APPLICATION INFORMATION**

These attenuators require a DC reference to ground. They may not operate properly when AC coupled on both the RF input and output without a DC ground reference provided as part of the circuit. See Application Note AN311.

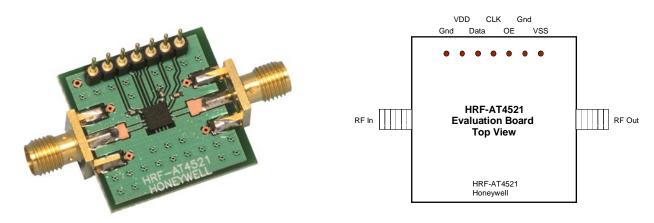

# **EVALUATION CIRCUIT BOARD**

Honeywell's evaluation board provides an easy to use method of evaluating the RF performance of our attenuator. Simply connect power, DC and RF signals to be measuring attenuator performance in less than 10 minutes.

HRF-AT4521 Evaluation Board

### **EVALUATION CIRCUIT BOARD LAYOUT DESIGN DETAILS**

| Item           | Description                                                    |

|----------------|----------------------------------------------------------------|

| РСВ            | Impedance Matched Multi-Layer FR4                              |

| Attenuator     | HRF-AT4521 Digital Attenuator                                  |

| Chip Capacitor | Panasonic Model ECU-E1C103KBQ Capacitor, .01uf 0402 10% 16V    |

| RF Connector   | Johnson Connectors Model 142-0701-801 SMA RF Coaxial Connector |

| DC Pin         | Mil-Max Model 800-10-064-10-001 Header Pins                    |

### **ORDERING INFORMATION**

| Ordering Number  | Delivery Method  | Units Per Shipment  |

|------------------|------------------|---------------------|

| HRF-AT4521-GR-TR | Tape and Reel    | 2500 Units per Reel |

| HRF-AT4521-GR-T  | Tape             | <2500               |

| HRF-AT4521-E     | Evaluation Board | One Board Per Box   |

The new –GR attenuators will replace and are fully back-compatible with the –AU attenuators.

## FIND OUT MORE

For more information on Honeywell's Microwave Products visit us online at **www.honeywell.com/microwave** or contact us at 800-323-8295 (763-954-2474 internationally).

Honeywell reserves the right to make changes to improve reliability, function or design. Honeywell does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

Honeywell 12001 Highway 55 Plymouth, MN 55441 Tel: 800-323-8295 www.honeywell.com/microwave

Form #4521W September 2007 ©2007 Honeywell International Inc.